使用Verdi 代替VCS 查看波形

使用VCS 生成FSDB, Verdi 打开FSDB

使用VCS 生成FSDB 波形文件

编译工程

|

|

运行 simv 生成fsdb

|

|

my_verdi.tcl 主要用于指定控制生成fsdb 的行为, 内容如下:

|

|

使用Verdi 打开fsdb

|

|

当打开fsdb 之后, 如果设计改变了, 只需要重新生成 fsdb 文件, 然后在Verdi 中按Shift+l 即可Reload Design 非常方便

完整的Makefile 示例

|

|

my_verdi.tcl 内容如下:

|

|

运行 make vcs_verdi_fsdb 可以编译并生成 fsdb 文件

运行 make verdi 可以查看fsdb 波形

在打开Verdi 后, 如果设计改变了, 只需要重新 make vcs_verdi_fsdb 然后再Verdi 中 Shift + l 即可 Reload Design 非常方便

Interactive Debug With Verdi (使用VCS 编译生成simv 然后 vcs 调用 verdi 查看波形)

编译生成 simv

|

|

调用 verdi 查看波形

|

|

这种方法运行仿真后会生成默认的 inter.fsdb , 感觉不怎么灵活

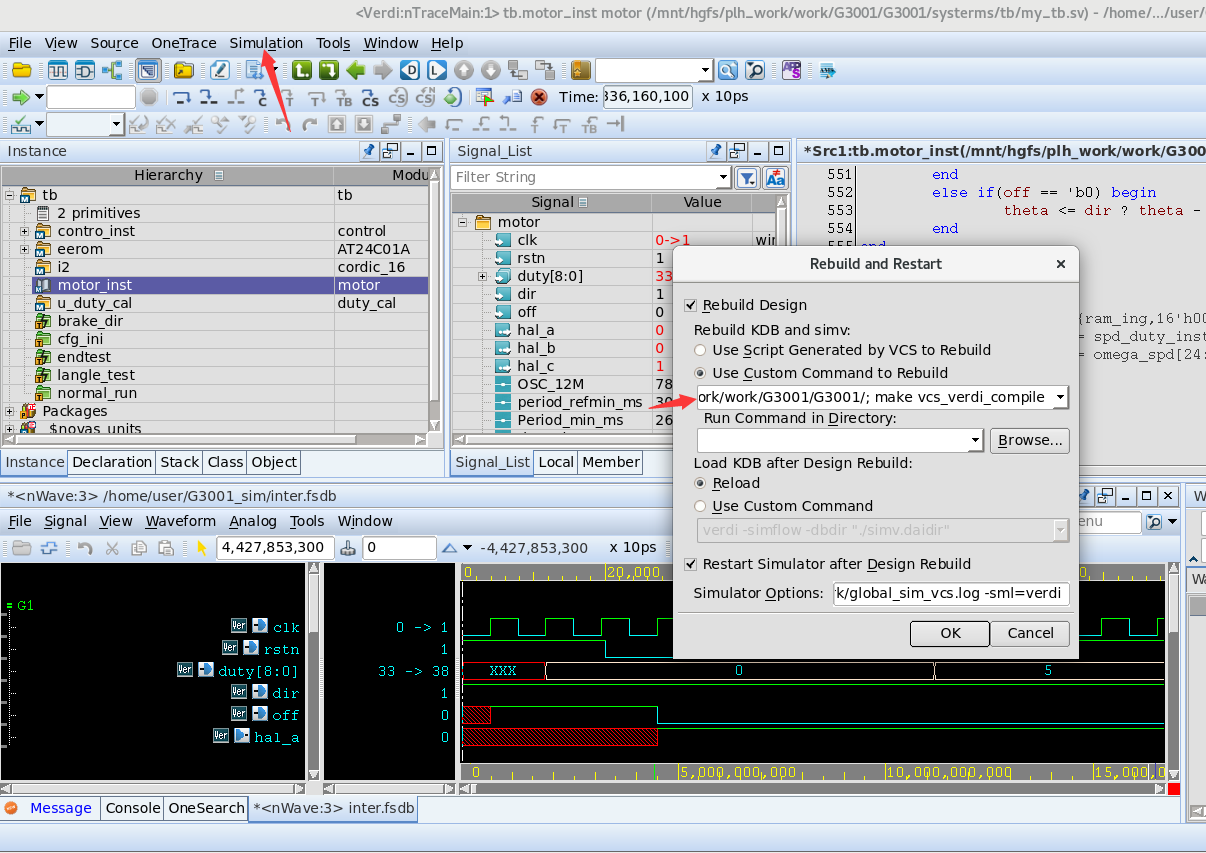

如果设计改变的话, 可以在Verdi 中Simulation -> Rebuild and Restart

Custom Command 如下:

|

|

先进入到Makefile 所在的目录再make 目标

完整Makefile 见完整的Makefile 示例

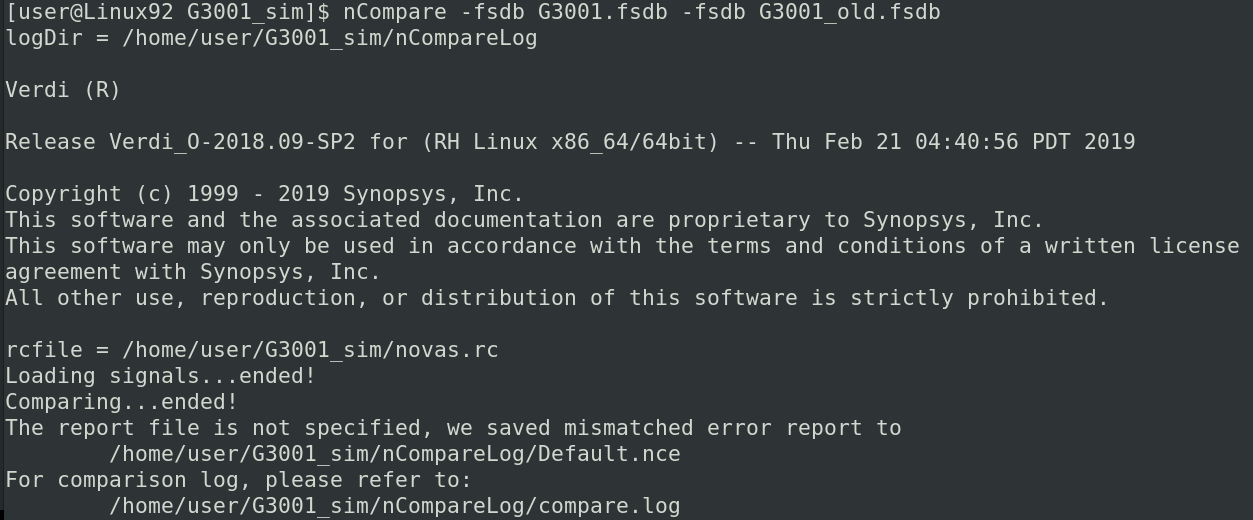

使用 nCompare 对比fsdb波形

生成差异信息

|

|

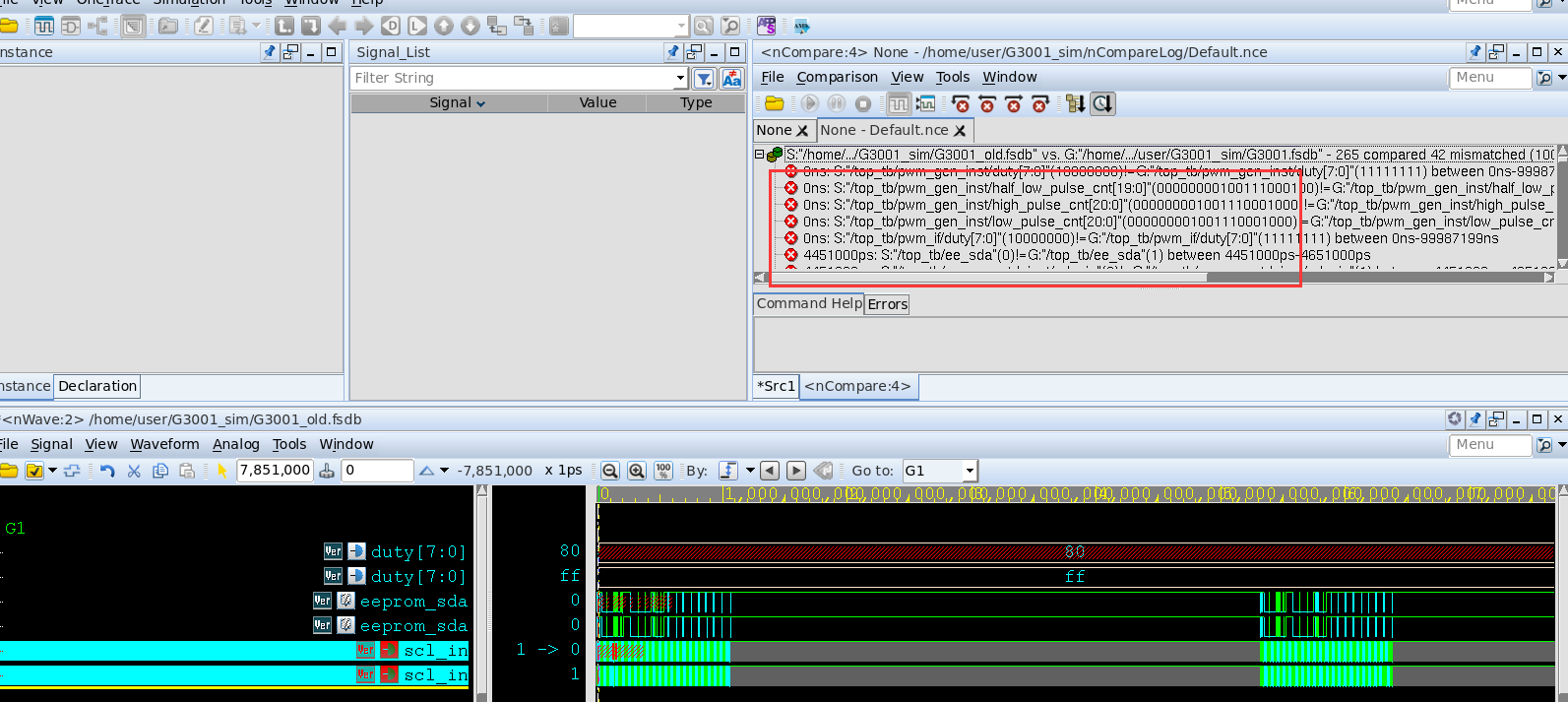

这会生成 nCompareLog 文件夹, 里面比较有用的是 Default.nce 这个是错误文件

这会生成 nCompareLog 文件夹, 里面比较有用的是 Default.nce 这个是错误文件

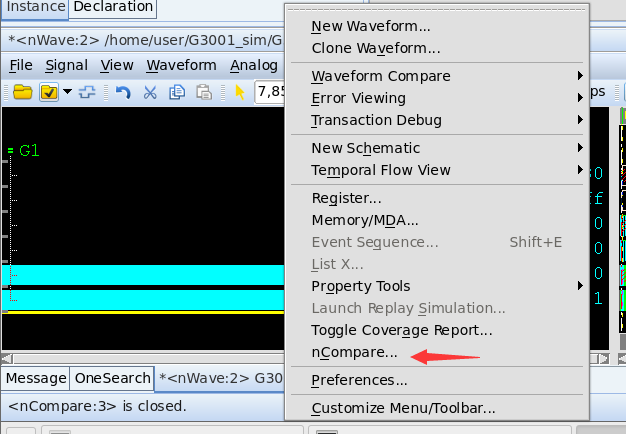

使用Verdi 查看波形差异

-

打开Verdi

-

打开波形窗口

-

在波形窗口下 Tools => nCompare

-

在nCompare 窗口 File => Open Err File 打开生成的 .nce 文件

双击差异信号可以在波形窗口中查看差异

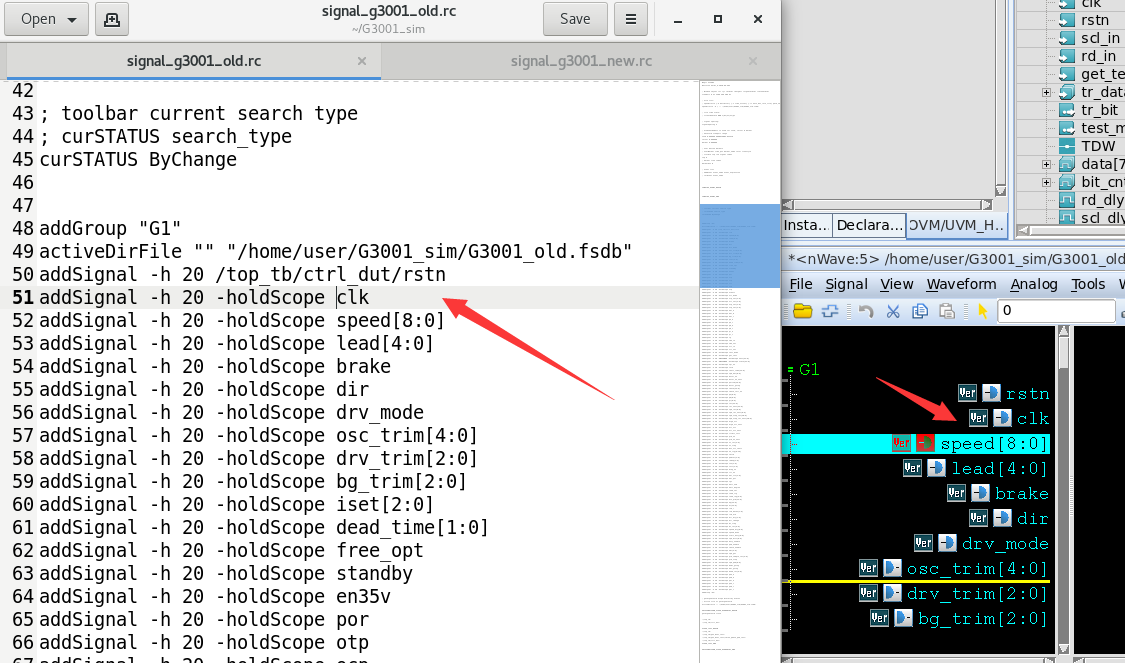

nWave 打开信号(signal)文件(xxx.rc) 并把信号重新排序

保存信号到文件

File => Save Signal 保存为 .rc 文件

编辑信号文件

假如想要对nWave 中的信号进行排序整理有两种方法:

假如想要对nWave 中的信号进行排序整理有两种方法:

- 一种办法是直接在nWave 里拖信号或者用m 移动到黄线处

- 直接编辑保存好的信号文件, 然后关闭波形窗口, 再新建一个nWave 窗口再打开 .rc 即可看到效果

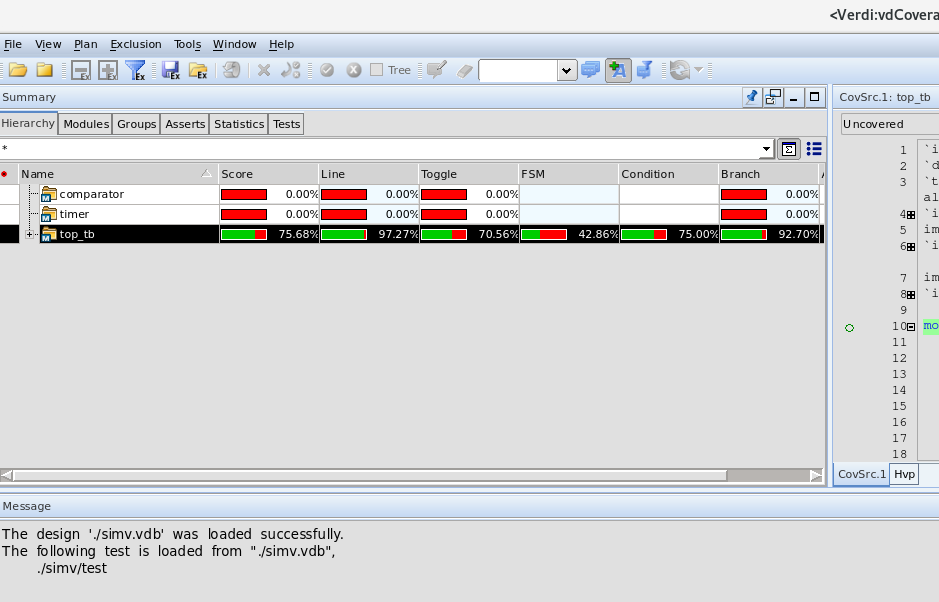

查看覆盖率 (Verdi Coverage)

生成覆盖率

VCS 版本大于等于 2013.06

在编译时加入使能参数

|

|

-debug_pp -P $(VERDI_HOME)/share/PLI/VCS/LINUX64/novas.tab \

$(VERDI_HOME)/share/PLI/VCS/LINUX64/pli.a -cm line+tgl+fsm+cond+branch+assert

其中 -debug_pp -P $(VERDI_HOME)/share/PLI/VCS/LINUX64/novas.tab $(VERDI_HOME)/share/PLI/VCS/LINUX64/pli.a 指定了生成覆盖率需要的文件路径

-cm line+tgl+fsm+cond+branch+assert 指定了要收集哪些覆盖率

- line

源代码覆盖率 - tgl

信号翻转覆盖率 - fsm

状态机覆盖率 - cond

条件 覆盖率 - branch

分支覆盖率 - assert

断言覆盖率

在跑仿真时加入使能参数

|

|

如果代码中有包含 UPF 文件, 还需要加入 -power=coverage+dump_hvp

|

|

必须拥有Verdi license 🙂

查看覆盖率

|

|

上面那条而今只是打开了Verdi 的查看覆盖率的GUI 并没有导入数据库, 需要 File => Open database

下面那条命令是直接打开数据库可以立即看到覆盖率

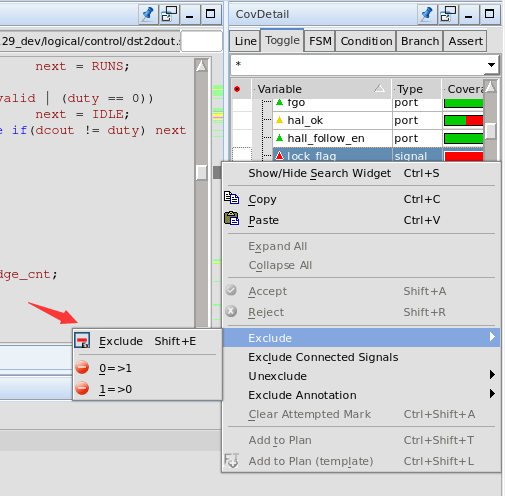

忽略信号 ( excusion signal )

通常有一些常量被赋值给了 多bit 的 wire 或者 reg 就会导致有一些bit 是绝对不可能覆盖到翻转的

可以把这些信号排除在覆盖率检查上

在CovDetali 窗口中对着信号右键 => Exclude => Exclude

在源码窗口选中信号 右键 => Exclude 或者直接用快捷键 Shift + E

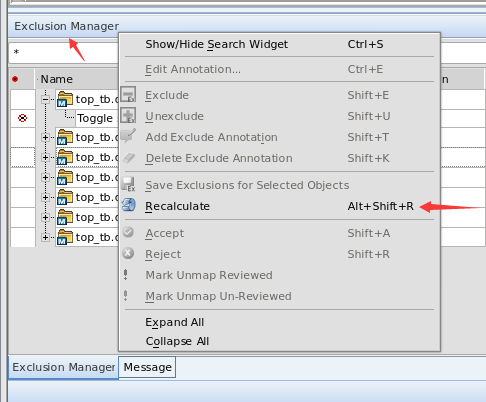

重新计算覆盖率

在Exclusion Manager 中右键 => Recalculate

把Exclusion 信号保存为文件 然后再Load 即可

File => Save all Exclusions

File => Load Exclusions => Load Exclusions from file

合并多个 coverage db (merge multile multi coverage db )

|

|

或者 使用 filelist

|

|

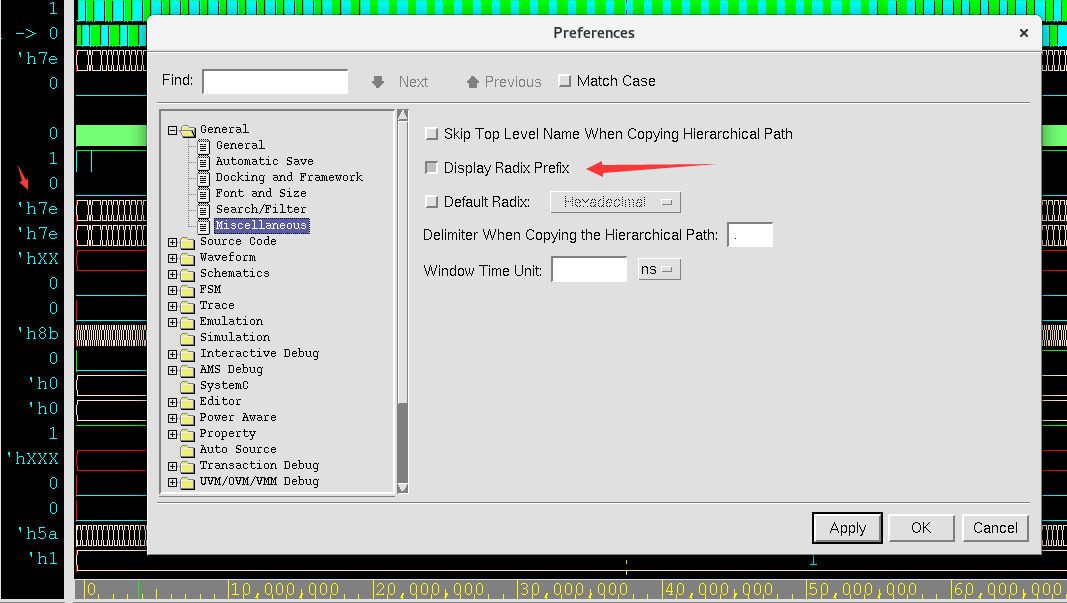

波形窗口显示Radix prefix

Tools => Preferences => General => Miscellaneous 勾选 Display Radix Prefix

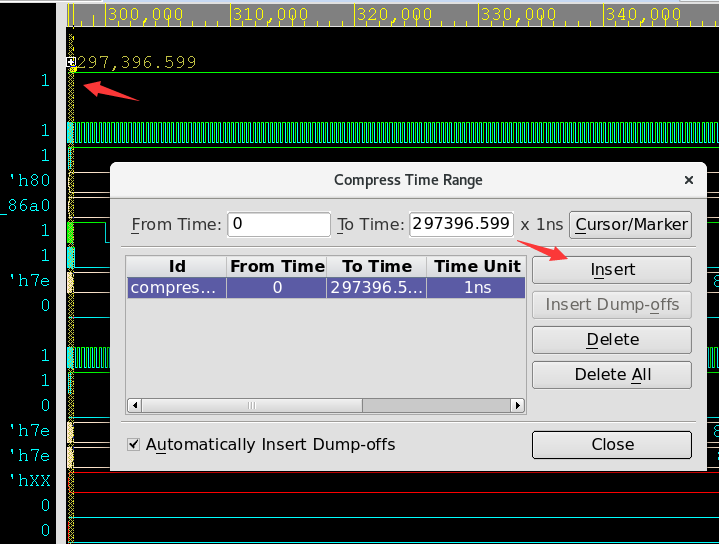

折叠一段波形 ( compress Time Range )

nWave 窗口下 View => Compress Time Range 然后填好时间后点Insert 就可以看到对应时间内的波形已经被折叠了

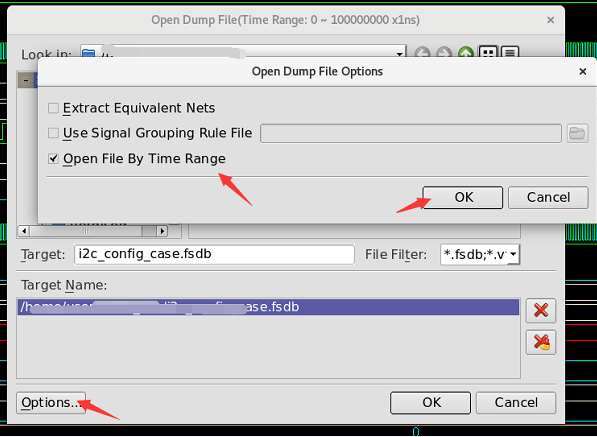

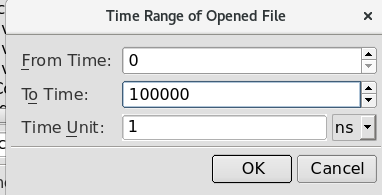

打开一段时间的波形 (open Dump File Time Range)

File => Open

需要改变显示时间范围的话可以 File => Set View Time Range

添加波形的几种方法 (add waveform)

默认添加module 下的所有信号( 除端口外还有本地信号 ) Include Local Signal

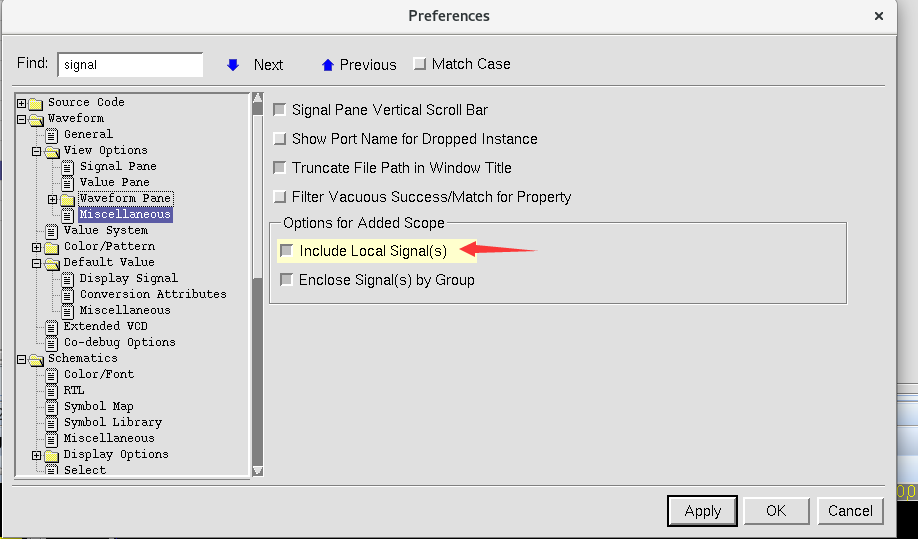

Tools => Preferences => Waveform => View Options => Miscellaneous => 选中 Include Local Signal(s)

不过这样选了之后, 加进去的波形的顺序会乱掉...

不过这样选了之后, 加进去的波形的顺序会乱掉...

直接从Instance 窗口加

直接从源码加

可以选中一段代码, 直接拖到波形窗口( 或 Ctrl + w ), 或者鼠标放在信号上按Ctrl+w

在Signal 窗口加

通过OneSearch 快速查找到信号然后双击跳到源码窗口, 进而拖到波形窗口

通过Find Scope (Shift + s) 或者 Find Signal (Shift + a) 查找信号之后按Ctrl + w

调试Glitch

编译选项

|

|

1 是指一个 timescale 的 timeunit, 并且一定要是整数, 如果`timescale 1ns/1ps 的话, -cm_glitch 就是指过滤掉不超过1ns 的毛刺

一般来说-cm_glitch 1 是默认的数值, 也是推荐值

因为当使用 -cm_glitch 0 的时候, delta 里面必须是四舍五入后为0 实际情况是, delta 0 cycle 里面不是真正的0, 信号必然有先后顺序,

当波形中所谓的delta 0 很接近于0.1 ( 也可能是0.01 ) 的时候, 就不会还是 -cm_glitch 0 能够过滤掉的了, 所以, 一般情况下还是使用 -cm_glitch 1

如果时钟频率大于1 G 的话需要把timescal 设成 100ps/1ps

运行选项

|

|

+fsdb+delta 等价于 +fsdb+glitch=0 +fsdb+sequential +fsdb+region

快速查找信号的memory 值

在源码中选中信号=> 右键 => Debug Memory => Show Memory Contents

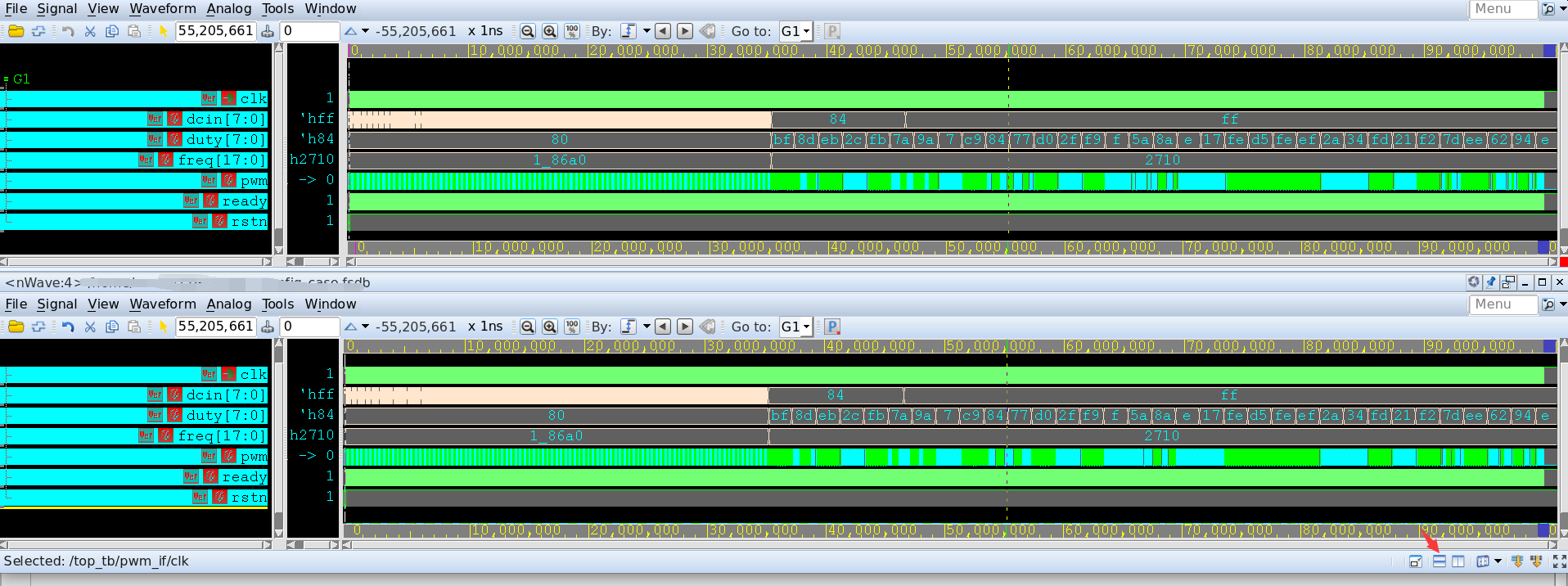

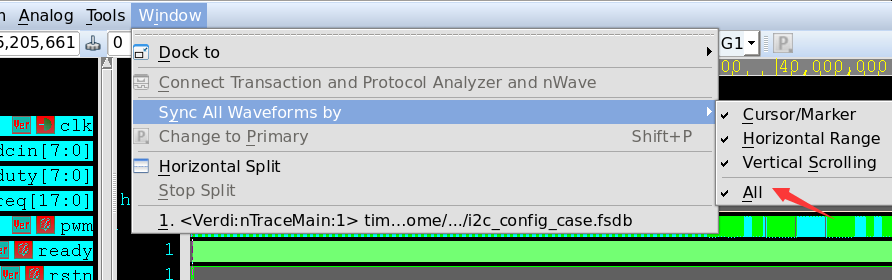

快速对比两个fsdb (compare fsdb)

打开一个新的Verdio 不包含设计 ( 即直接命令行敲verdi )

打开第一个fsdb 放到一个容器里

nWave => Window => Dock to => New Container Window

打开第二个fsdb 放到第一个fsdb 所在的容器里

横向分屏

开启同步功能

快速获得一个信号的值 (fsdbreport)

使用 fsdbreport 工具

|

|

使用 fsdbreport 成功之后会生成一个 report.txt 文件, 里面记录了目标信号的所有值

Examples:

-

Assign the begin time and end time for the report.

%fsdbreport verilog.fsdb -s /system/addr -bt 1000ps -et 2000ps -

Report a slice of a bus signal.

%fsdbreport verilog.fsdb -s “/system/addr[7:4]” -

Report signals in the signal list with different formats.

%fsdbreport fsdb/vhdl_typecase.fsdb -nocase -s top/A_SIMPLE_REC.FIELD3

-a simple.field3 -w 15 TOP/A_COMPLEX_REC.F1.FIELD3 -a complex.f1.field3

-w 20 top/a_std_logic_vector -af sean2.alias -of a -o output.txt

-bt 1000 -et 2000 -

Report a scope and its descendants. Multiple scopes may be specified.

%fsdbreport rtl.dump.fsdb -bt 10 -et 100 -s “/system/i_cpu/*”

-level 3 /system/i_pram/clock -cn 0 -

Report the results for the specified strobe point using -strobe.

%fsdbreport verilog.fsdb -strobe “/system/clock==1” -s /system/data

/system/addr -

Report the results when the expression value changes to true.

%fsdbreport verilog.fsdb -exp “/system/addr==‘h30 & /system/clock==1”

-s /system/data -

Report the force, release or deposit information of the specified signals using -find_forces.

%fsdbreport rtl.fsdb -find_forces -s “/system/i_cpu/*” -level 2 -o report.txt -

Report the force of the specified signals using -find_forces and -exclude_scope.

%fsdbreport rtl.fsdb -find_forces -s “/system/i_cpu/*” -exclude_scope “/system/i_cpu/s1/*” “/system/i_cpu/s2” -o report.txt

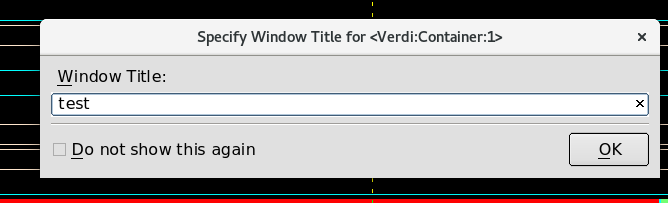

设置Verdi 的Title

启动项中加入 -preTitle xxx 可以设置当前title

在波形窗口把某一个信号导出到文件

选中信号

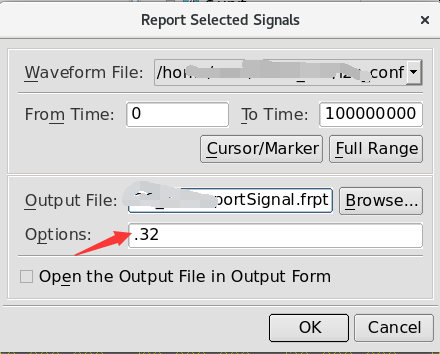

nWave => File =>Report Selected Signals

箭头处是设置位宽, 如果数据比较小的话可以不设, 默认只有9 位

使用Verdi 调试约束 ( constains )

|

|

直拉交互模式 或者 进入verdi 之后 Window => Interactive Debug Mode

dump 数据到 fsdb

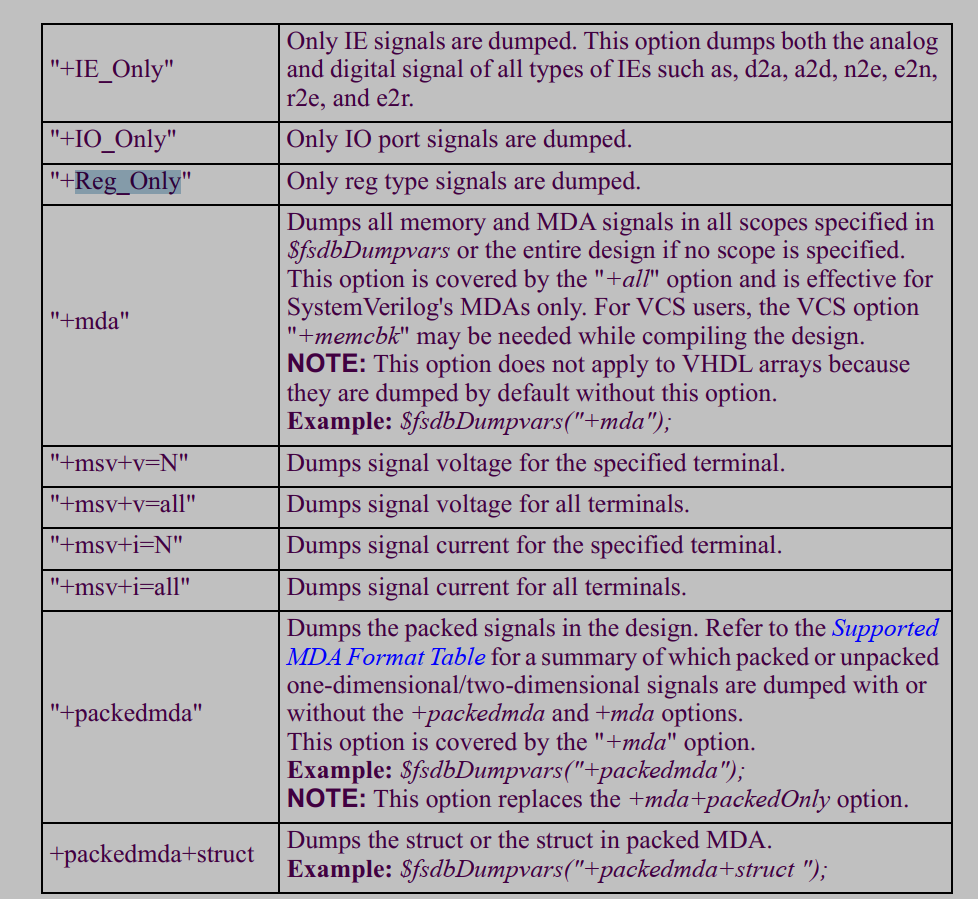

可用于约束Dump 的类型有:

把所有寄存器Dump 到 fsdb

- 在TCL 中或者源文件中

1$fsdbDumpvars("Reg_Only") - 使用 runtim option : ./simv +fsdb+reg_only

- 设置环境变量

setenv FSDB_REG_ONLY 1

只Dump 指定路径下的信号

|

|

其中:

- 0: all signals in all scopes

- 1: all signals in current scopes

- 2: all signals in current scopes and all scopes one level below

- n: all signals in current scopes and all scopes n-1 level below

指定 fsdb 文件名

|

|

Verdi 显示状态机的名字

对于本身是parameter 或者 enum 定义的状态机变量, 可以直接设置Radix 为 ASCII 或者 Enum 即可

另一种办法

在Instance 中选中含有状态机的module 然后 Tools => Extract Interactive FSM => All Stages => OK

然后在出现的状态机上面按鼠标中键之把状态机拖到nWave 窗口即可 ( 不过我没有成功, 可能是状态机不规范… )