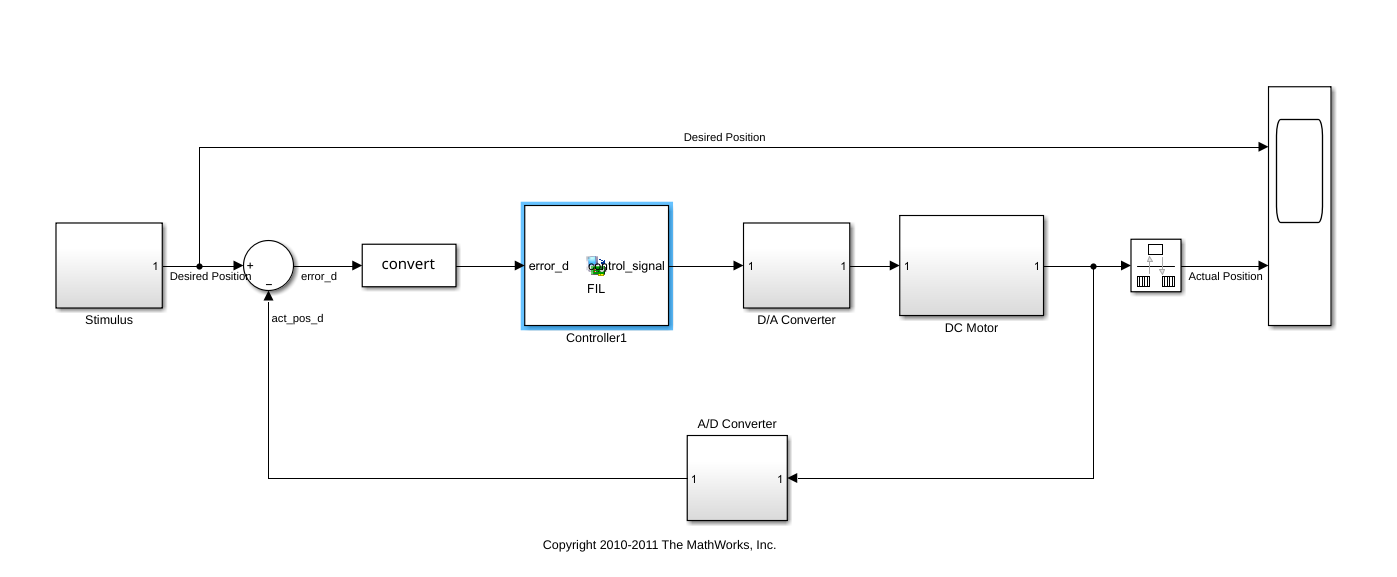

FIL 的概念是把FPGA 接入到 Simulink 仿真环境中, Simulink 生成的激励通过JTAG 把激励灌到FPGA 里,

然后再通过JTAG 把结果返回给 Simulink, 除了用JTAG 通信外还可以通过网络来交换数据

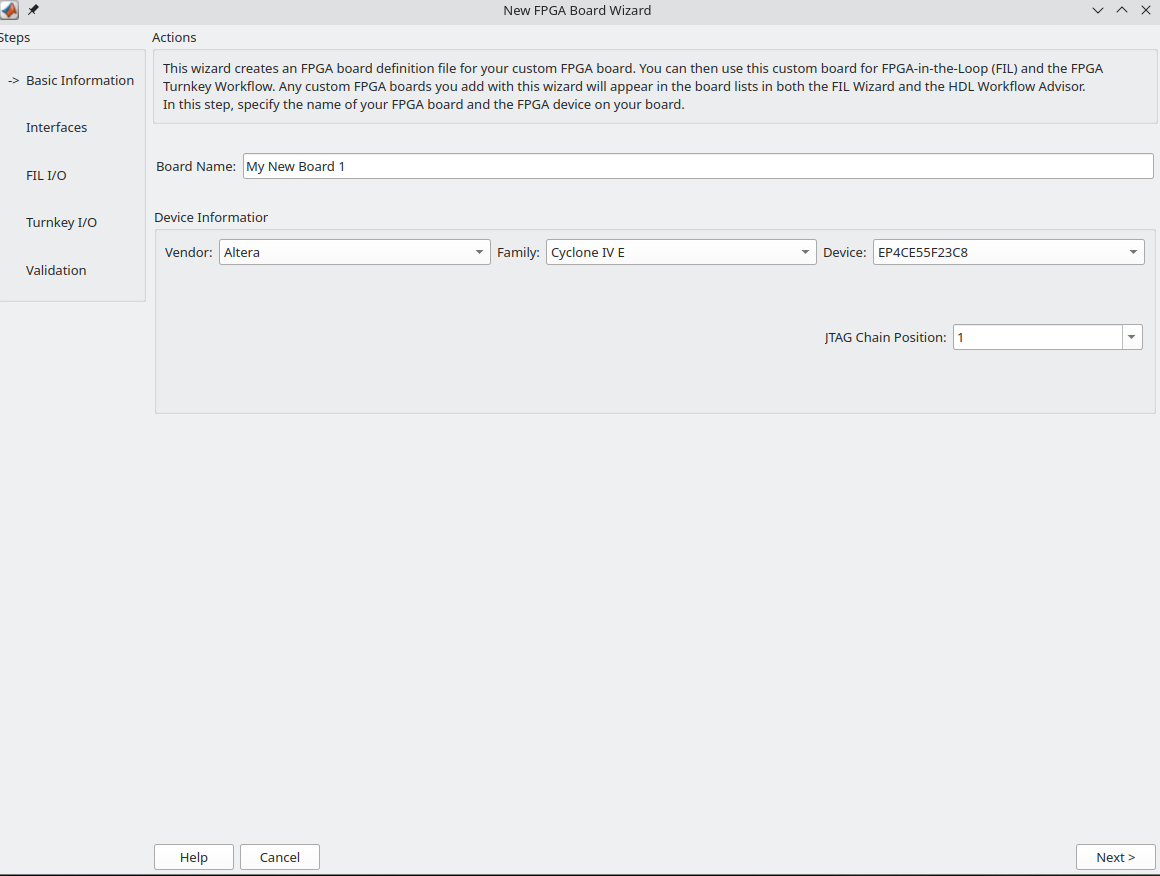

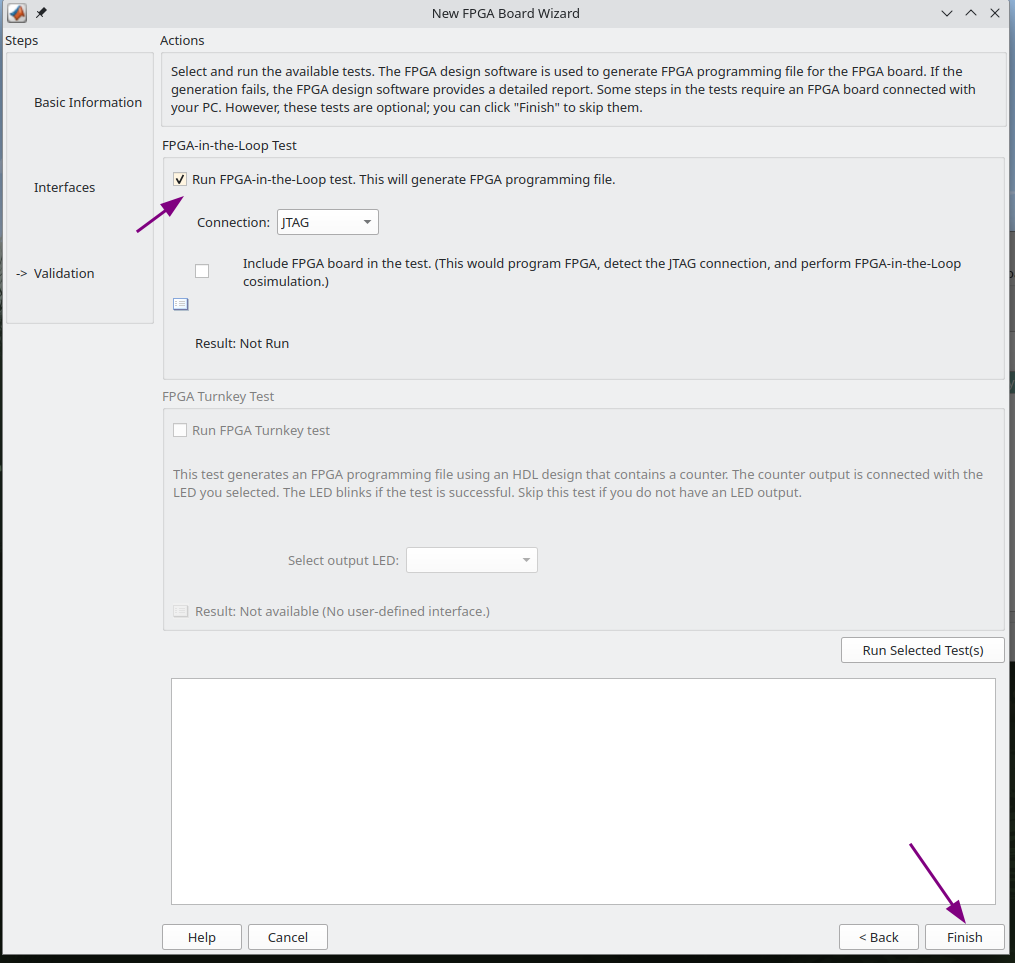

FIL New FPGA Board

新建板子参考: New FPGA Board Wizard 和 Create Xilinx KC705 Evaluation Board Definition File

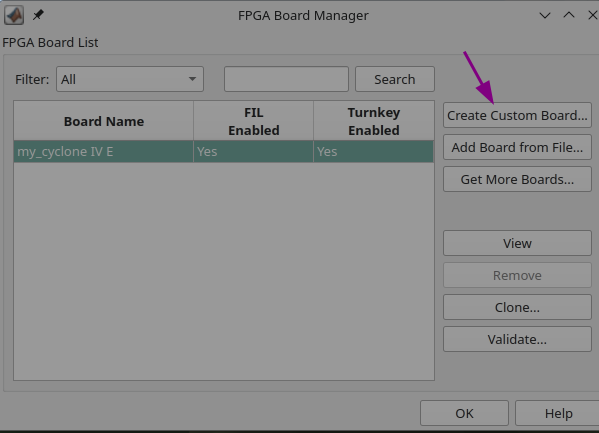

在 Matlab 输入 fpgaBoardManager 打开 FPGA Board Manager

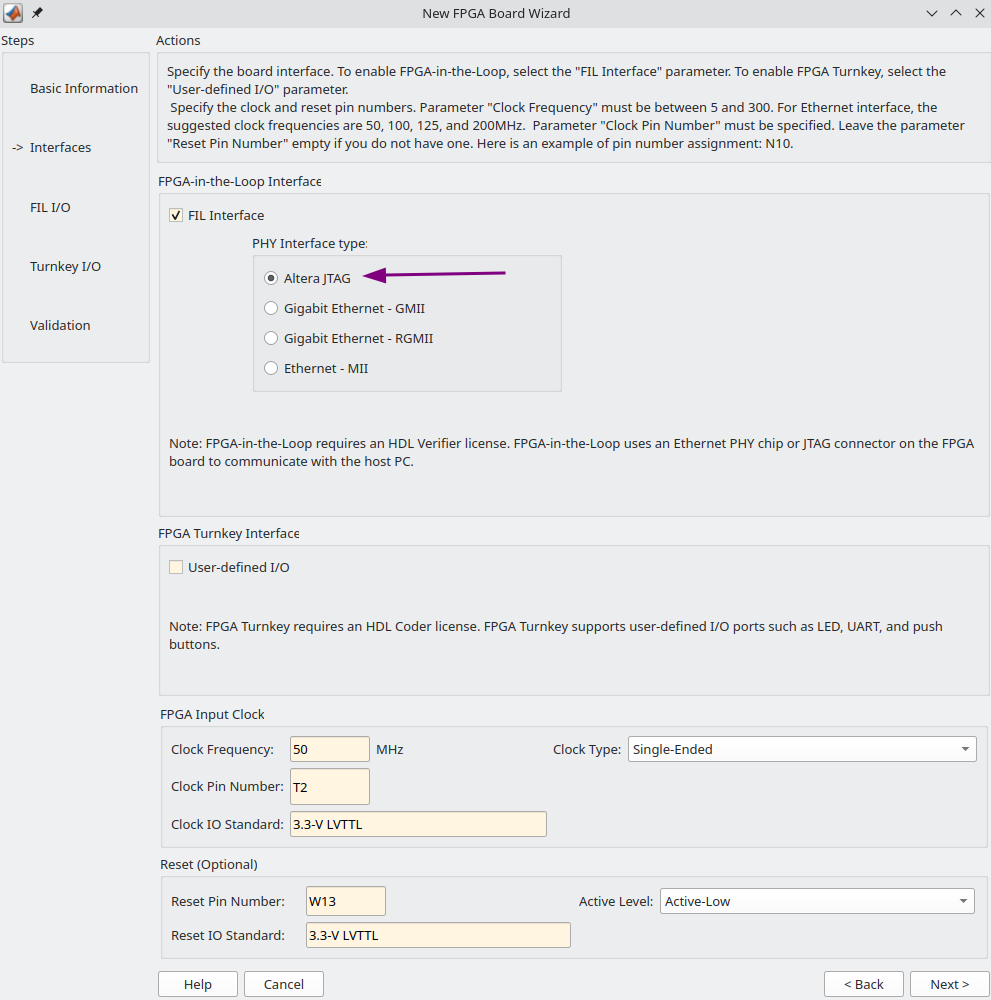

FIL 接口这里为了方便就选JTAG 了, 即使用仿真器来在Matlab 和 FPGA 中建立通讯

当然也可以选择 Ethernet, 但是这个需要填的IO 会比较多

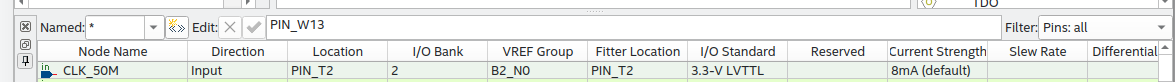

IO Standard 是根据真实的 Quartus 工程填的, 貌似也可以留空

可以看到新建板子只需要要指定时钟, 复位脚, 以及时钟频率, 以及通讯方式即可

利用FIL 仿真PID

参考: Verify HDL Implementation of PID Controller Using FPGA-in-the-Loop

启动 Matlab

|

|

由于我是在Linux 上运行Matlab, 如果不设置 LD_LIBRARY_PATH 的话, 会报 " Failed to load shared library libsld_hapi_dll_loader.so " 的错误

但是又不想加到 ~/.zshrc 里, 因为这样会影响别的软件, 就只有在启动 matlab 的时候临时指定 LD_LIBRARY_PATH

打开 fil_pid.slx

在Matlab 上运行

|

|

这会打开 fil_pid 的工程, 双击 fil_pid.slx

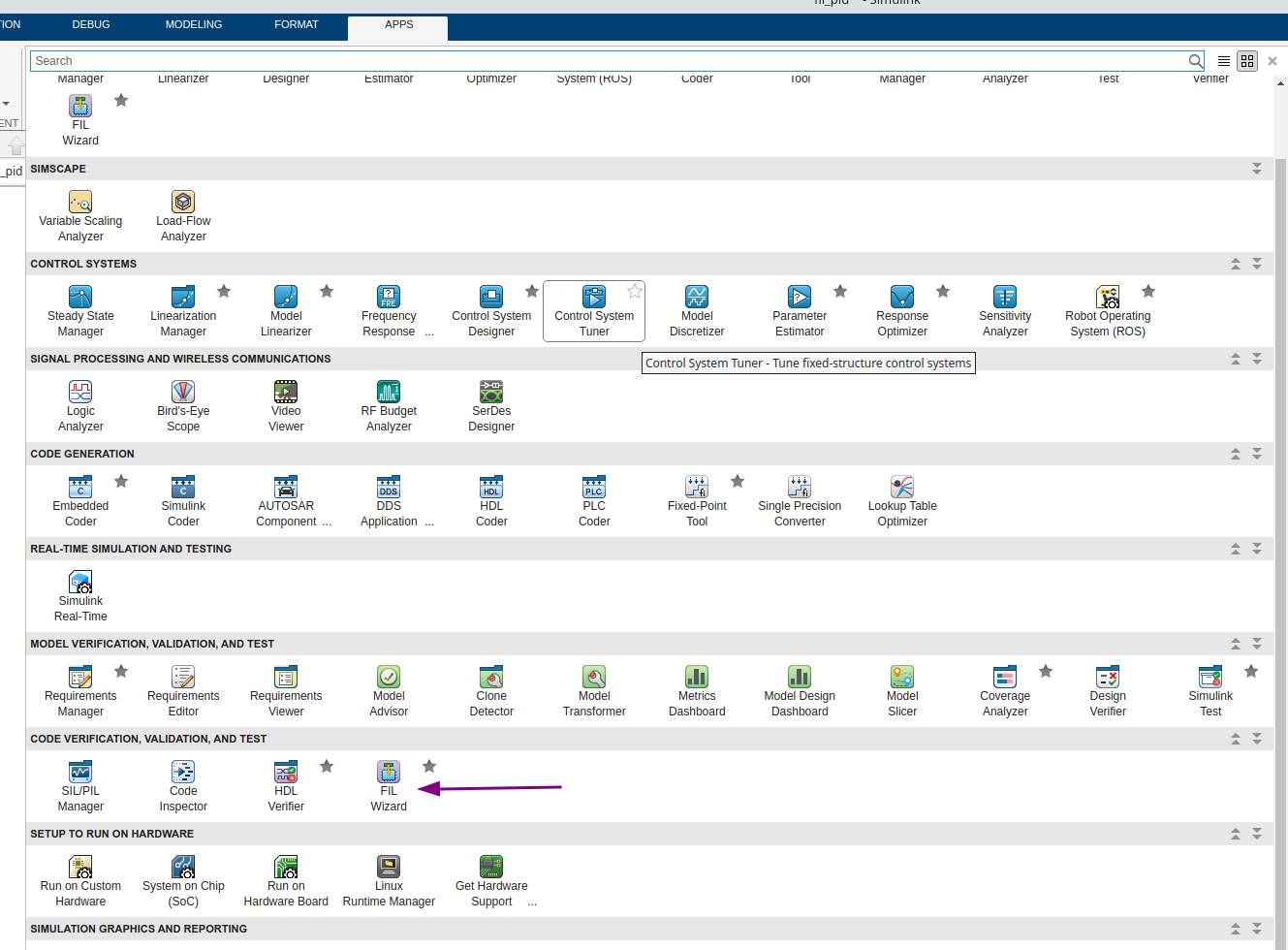

在APPS 里找到 FIL Wizard 进击进入

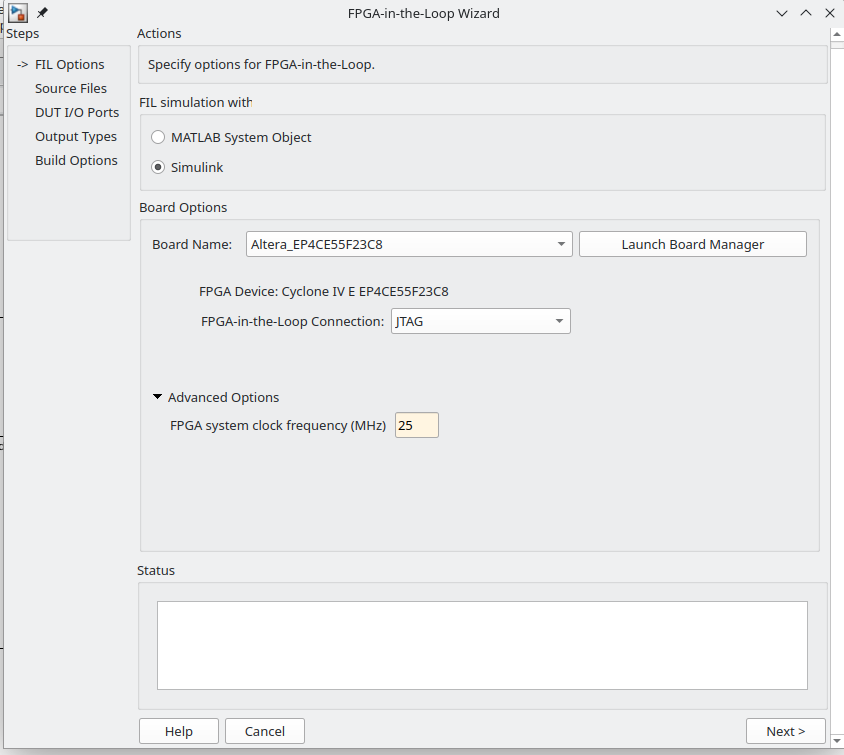

设置 FIL 选项

其中 Advanced Options 里面的时钟默认是25MHZ, 貌似改不了, 改了还有可能会报错

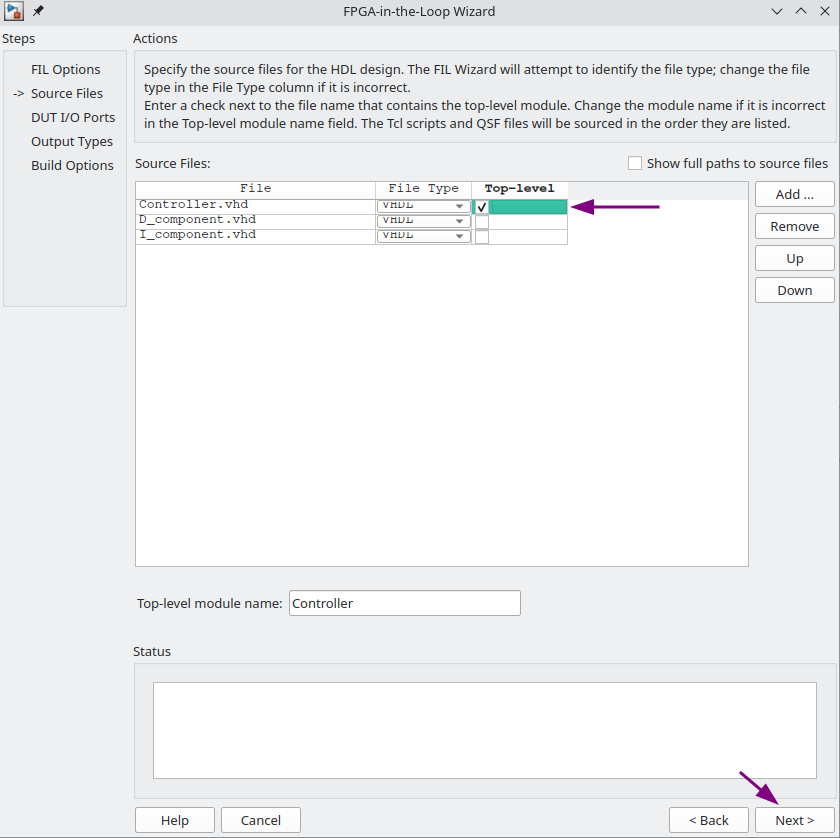

添加设计源文件

添加完源文件还需要把顶层文件标记为 TOP-level 才可以下一步

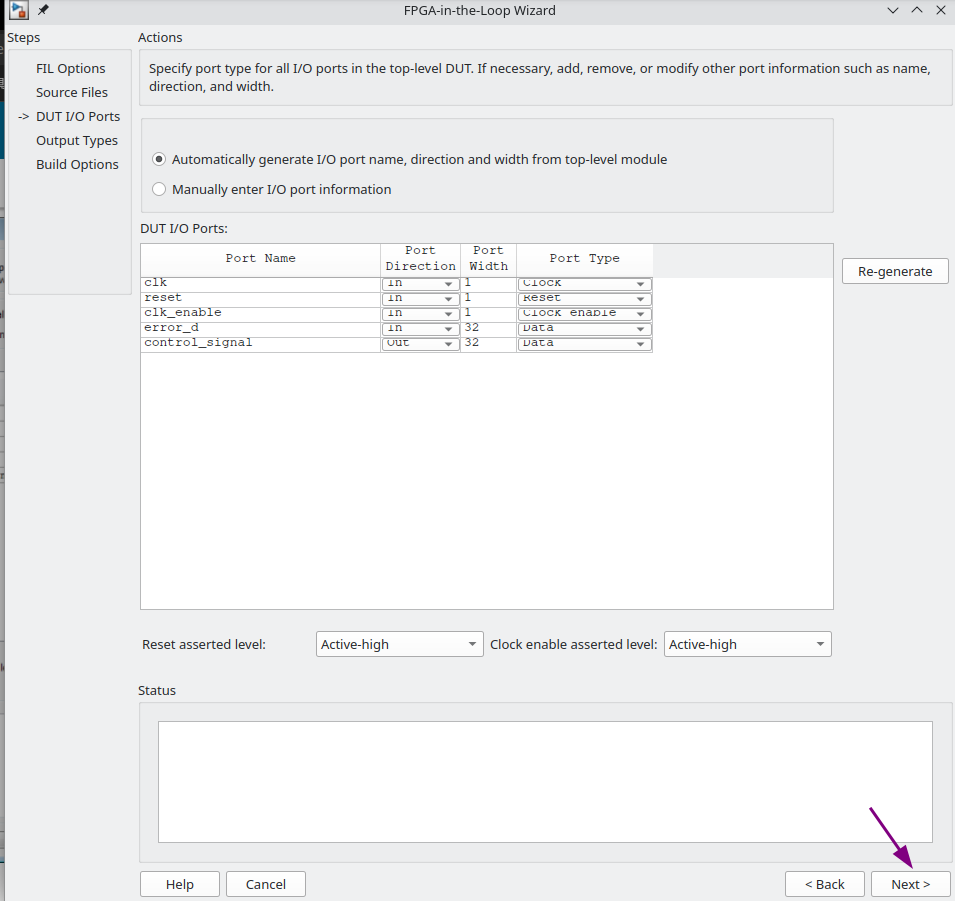

检查IO

没有问题就下一步

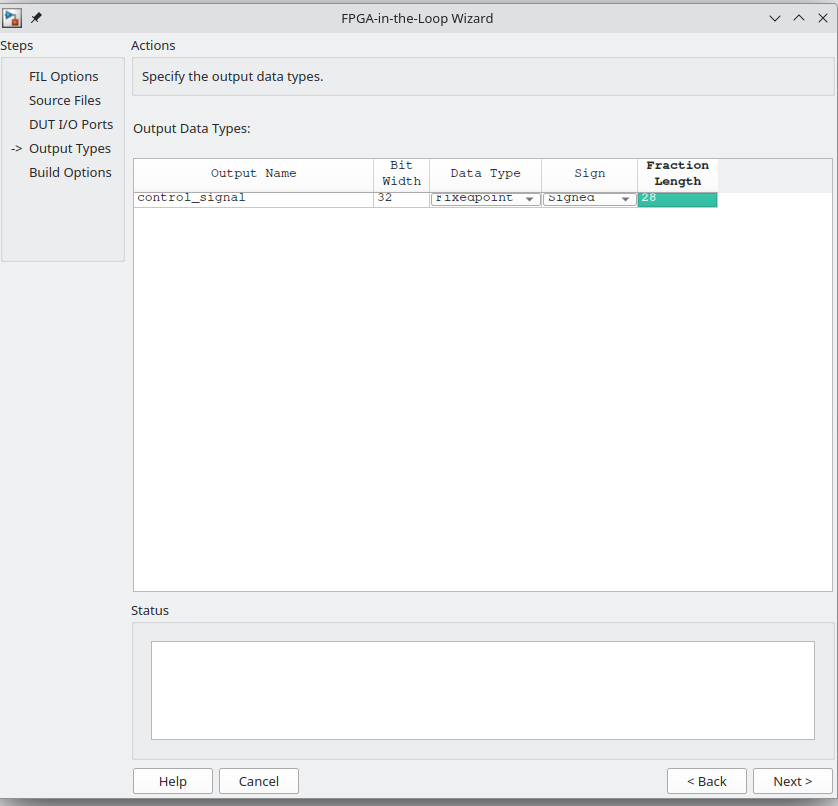

设置输出类型

结合源码, 把control_signal 设置为定点数, 有符号数, 分数部分为28 位, 只有这样FPGA 和 Matlab 才能正确的交换数据

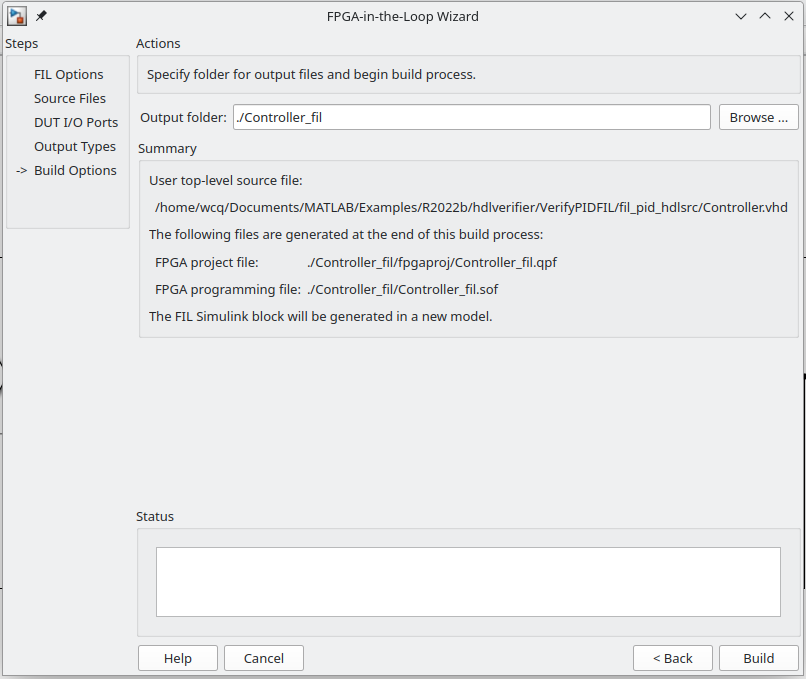

设置编译选项

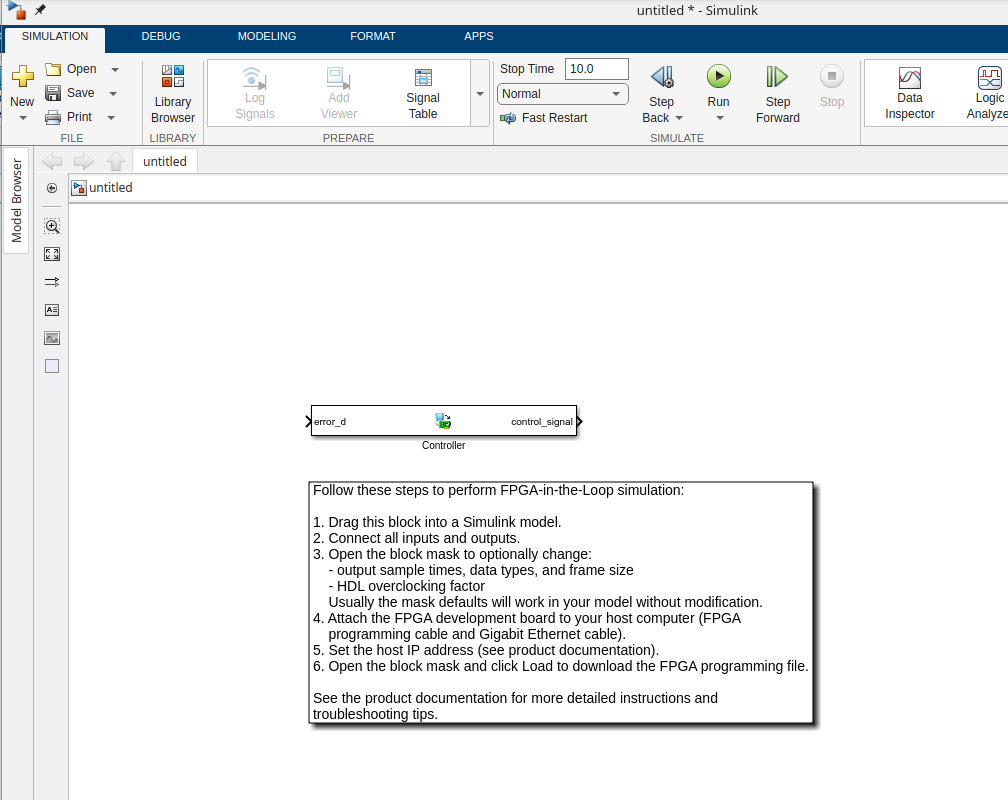

点击Build 之后, 一切顺利的话会弹出一个已经编译好的 FIL 模块

按照生成的 FIL 模块的提示, 把 FIL 模块拖到原PID 工程中并完成连线

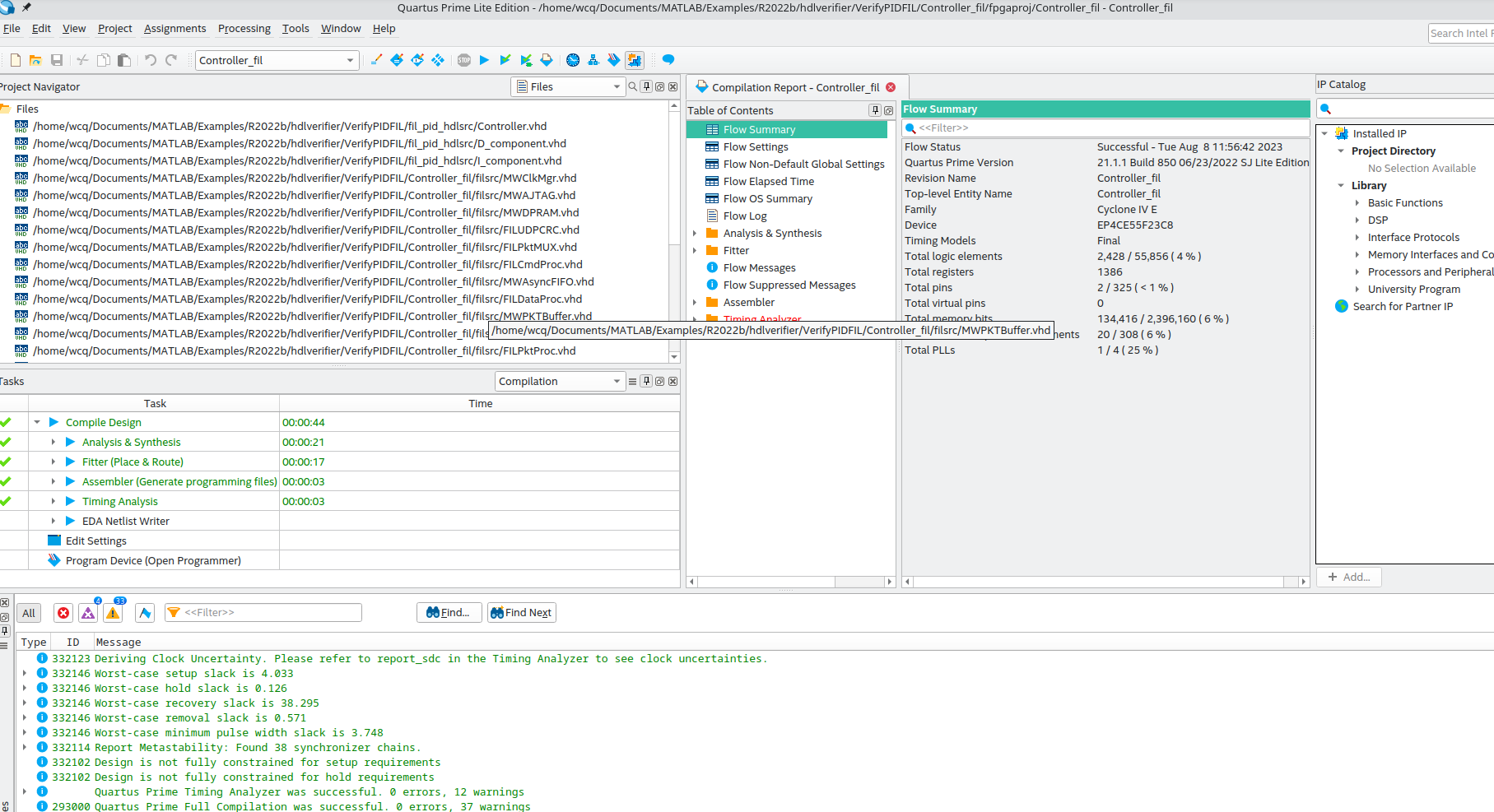

使用quartus 打开FIL 工程, 编译生成 sof

可以看到工程中加入了很多FIL 的文件

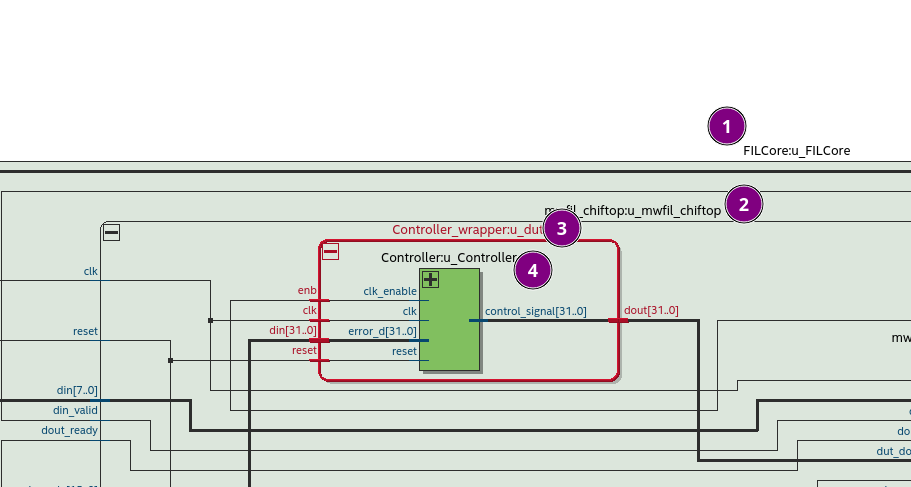

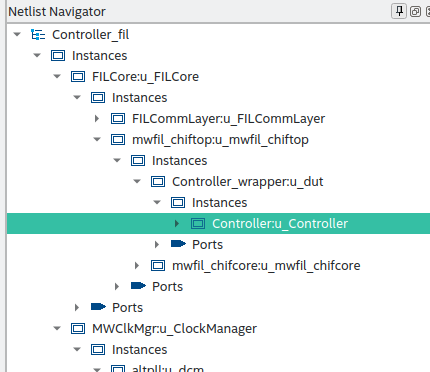

Tools => Netlist viewer => RTL Viewer

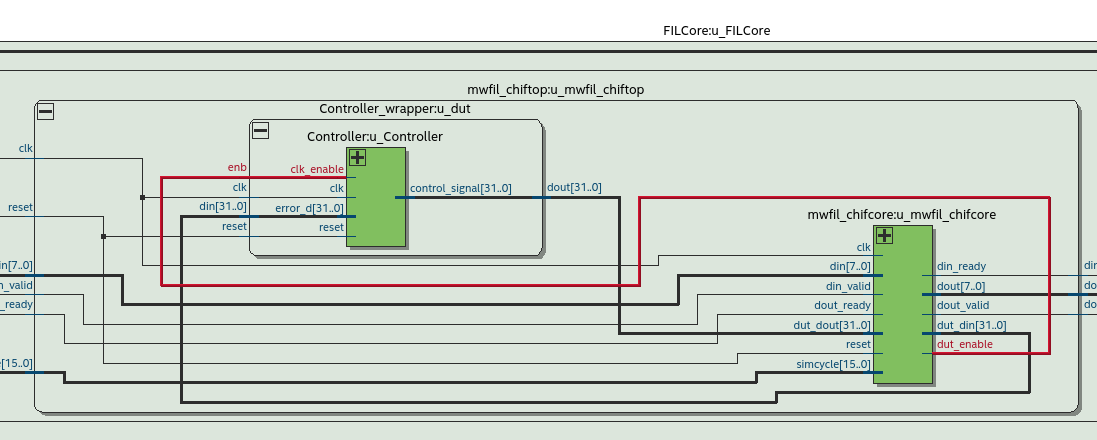

Controller 外面还包了几层, 分别是 FILCore => mwfil_chiftop => Controller_wrapper => Controller

其中 FILCore 还被 Controller_fil ( 真正的顶层 ) 包了

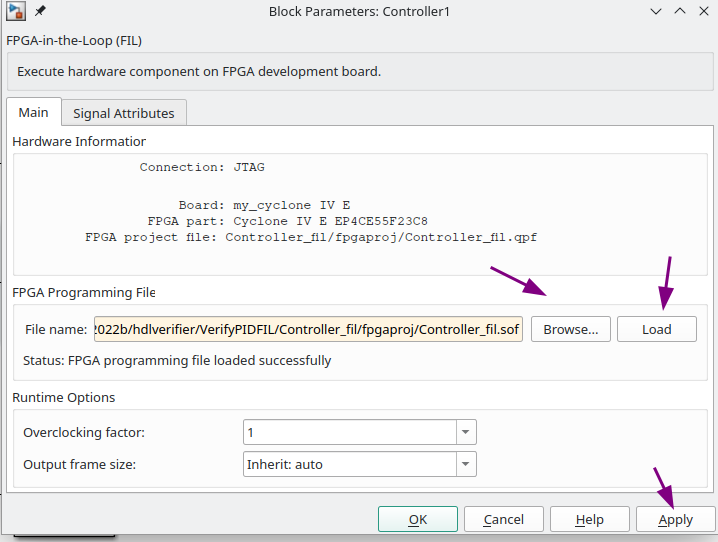

在Simulink 中双击 FIL 模块

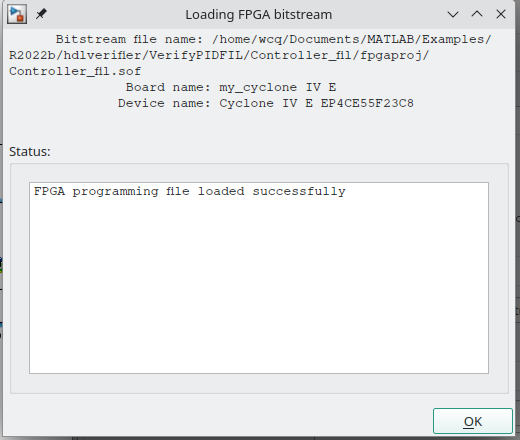

确保FPGA 已经上电并且正确连接了仿真器, 点击Browse 选择 sof 文件, 然后 Apply 再 Load, 这会把sof 下载到FPGA

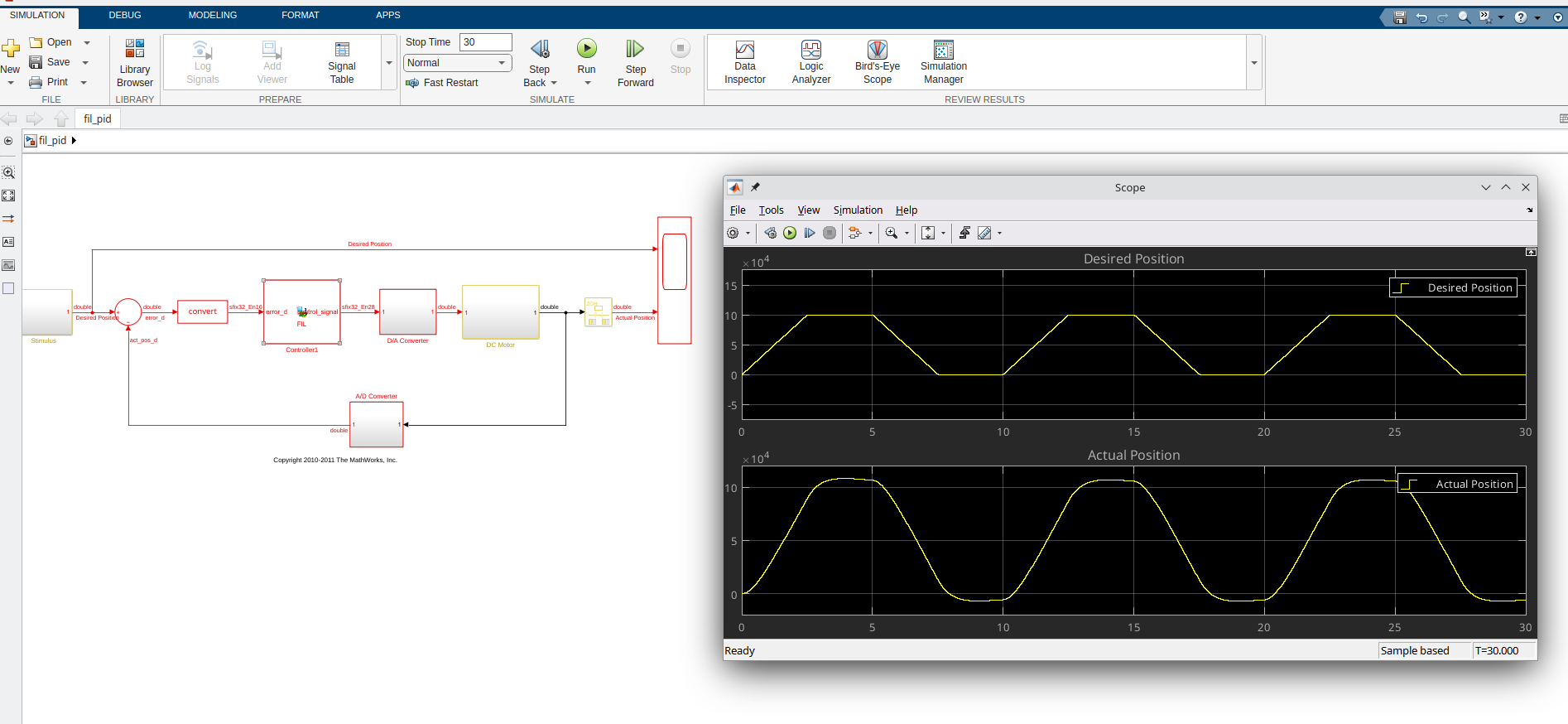

在Simulink 中点击仿真

等待一会儿, 打开示波器就可以看到波形了

总结

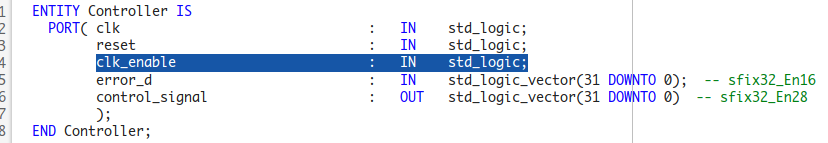

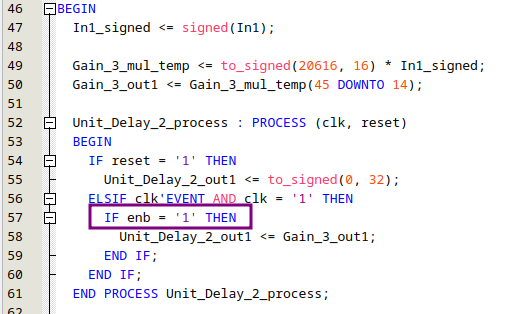

从simulink 中只能看到 FIL 只有一个输入( error_d ) 和一个输出(control_signal), 但是实际上在设计文件中还多了一个输入 (clk_enable)

这个也是必须的, matlab 就是通过控制这个clk_enable 来使得FPGA 和matlab 仿真的时间同步, 所以在设计上需要使用clk_enable 来控制FPGA 的时候的有效性

matlab 让FPGA 跑时, FPGA 才能跑

其中 enb 就是clk_enable